# Chapter 5

# CONTROL PANEL TYPE 49

|                                                                                                                                   |                                                     | LIS                                                              | ST C                  | OF CC                           | ONTERTS/                                                                                                                                           |         |          |                |                      |

|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------|-----------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------|----------------|----------------------|

|                                                                                                                                   |                                                     |                                                                  | Pare                  | a.                              |                                                                                                                                                    |         |          | Par            | ·a.                  |

| Introduction                                                                                                                      |                                                     |                                                                  |                       | 1                               | Operation                                                                                                                                          |         |          |                |                      |

| Description                                                                                                                       |                                                     |                                                                  |                       |                                 | General                                                                                                                                            |         |          |                | 14<br>15             |

| Description                                                                                                                       |                                                     |                                                                  |                       | 2 .                             | Vostage control<br>Frequency control                                                                                                               |         |          |                | 18                   |

| General                                                                                                                           | •••                                                 |                                                                  | • • •                 | 1 \                             | Servicing                                                                                                                                          |         | ., .,    |                |                      |

| Magnetic amplifiers                                                                                                               | • • •                                               | •••                                                              | • • •                 | 1/1/2                           | Output voltage and frequen                                                                                                                         | cy tes  | ts       |                | 21                   |

| Switching transistors                                                                                                             | •••                                                 | •••                                                              |                       | 8/                              | Fault location                                                                                                                                     |         |          |                | 22                   |

| Square wave generator                                                                                                             | •••                                                 |                                                                  | 1                     | 10/                             | Transistors and diodes                                                                                                                             |         |          |                | 26                   |

| Electrical circuits                                                                                                               | •••                                                 | •••                                                              | N                     | 1.1/                            | Capacitors                                                                                                                                         |         |          |                | 28                   |

|                                                                                                                                   |                                                     | ٨                                                                | $\mathfrak{d}^{p}/$   | /                               |                                                                                                                                                    |         |          |                |                      |

|                                                                                                                                   |                                                     | <i>V</i> 0                                                       | ZIST                  | OF T                            | TABLES                                                                                                                                             |         |          |                |                      |

|                                                                                                                                   |                                                     | . V                                                              |                       |                                 | Table                                                                                                                                              |         |          |                |                      |

|                                                                                                                                   | Det                                                 | ails of Co                                                       | mpon                  | ents                            | 1                                                                                                                                                  |         |          |                |                      |

|                                                                                                                                   | $\cap$                                              | N/                                                               |                       |                                 |                                                                                                                                                    |         |          |                |                      |

|                                                                                                                                   |                                                     | NIST.                                                            | OF                    | HIJI                            | STRATIONS                                                                                                                                          |         |          |                |                      |

|                                                                                                                                   |                                                     | 0                                                                |                       |                                 | SIMILIONS                                                                                                                                          |         |          | F              | ig.                  |

| Royal inverter and cont                                                                                                           | rolla                                               | വ്. /_                                                           | Fi                    | · .                             | Typical output characterist                                                                                                                        |         | Franconc |                | 18.                  |

| Moyul inverter and com                                                                                                            |                                                     | hell I vne                                                       | 49                    |                                 |                                                                                                                                                    | TO OT I |          |                |                      |

| General view of control                                                                                                           |                                                     | /                                                                | 49<br>                | 1 2                             | bridge                                                                                                                                             |         |          | <i>y</i><br>•  | 9                    |

| General view of control Control panel chassis—                                                                                    | panel                                               | /                                                                | 49<br>                |                                 | bridge  Theoretical circuit diagram                                                                                                                |         | <br>     | <i>y</i><br>   | 9<br>10              |

| General view of control<br>Control panel chassis—<br>Control panel chassis—                                                       | panel<br>Top                                        | /                                                                | 49<br><br>            | 2                               | bridge Theoretical circuit diagran                                                                                                                 |         |          | <i>y</i><br>•• |                      |

| Control panel chassis—                                                                                                            | panel<br>Top<br>Under                               | /                                                                |                       | 2 3                             | bridge Theoretical circuit diagram Wiring diagrams                                                                                                 |         |          | ••             |                      |

| Control panel chassis—<br>Control panel chassis—<br>Control panel chassis—<br>Block diagram of volta                              | panel<br>Top<br>Under<br>End<br>ge don              | /<br>/<br>side<br><br>trol circui                                | <br><br>              | 2<br>3<br>4                     | bridge Theoretical circuit diagram Wiring diagrams Top of control panel                                                                            |         |          |                | 10                   |

| Control panel chassis—<br>Control panel chassis—<br>Control panel chassis—<br>Block diagram of volta<br>Typical characteristic of | panel<br>Top<br>Under<br>End<br>ge don              | /<br>/<br>side<br><br>trol circui                                | <br><br>              | 2<br>3<br>4<br>5<br>6           | bridge Theoretical circuit diagram Wiring diagrams Top of control panel Underside of control panel                                                 |         |          |                | 10<br>11             |

| Control panel chassis— Control panel chassis— Control panel chassis— Block diagram of volta Typical characteristic of reactor L1  | panel<br>Top<br>Under<br>End<br>ge cont<br>curve fo | <br><br>side<br><br>trol circui<br>or saturab<br>                | <br><br>it<br>ble     | 2<br>3<br>4<br>5<br>6           | bridge Theoretical circuit diagram Wiring diagrams Top of control panel Underside of control panel Zener diode mounting brace                      |         |          |                | 10<br>11<br>12       |

| Control panel chassis—<br>Control panel chassis—<br>Control panel chassis—<br>Block diagram of volta<br>Typical characteristic of | panel<br>Top<br>Under<br>End<br>ge cont<br>curve fo | <br><br>side<br><br>trol circui<br>or saturab<br>                | <br><br>it<br>ble     | 2<br>3<br>4<br>5<br>6           | bridge Theoretical circuit diagram Wiring diagrams Top of control panel Underside of control panel Zener diode mounting brace                      | teket   |          |                | 10<br>11<br>12<br>13 |

| Control panel chassis— Control panel chassis— Control panel chassis— Block diagram of volta Typical characteristic of reactor L1  | panel<br>Top<br>Under<br>End<br>ge cont<br>curve fo | <br><br>side<br><br>trol circui<br>or saturab<br><br>ntrol circu | <br><br>it<br>ble<br> | 2<br>3<br>4<br>5<br>6<br>7<br>8 | bridge Theoretical circuit diagram Wiring diagrams Top of control panel Underside of control panel Zener diode mounting brace Diode mounting board | teket   |          |                | 10<br>11<br>12<br>13 |

| Control panel chassis— Control panel chassis— Control panel chassis— Block diagram of volta Typical characteristic of reactor L1  | panel<br>Top<br>Under<br>End<br>ge cont<br>curve fo | <br><br>side<br><br>trol circui<br>or saturab<br><br>ntrol circu | <br><br>it<br>ble<br> | 2<br>3<br>4<br>5<br>6<br>7<br>8 | bridge Theoretical circuit diagram Wiring diagrams Top of control panel Underside of control panel Zener diode mounting brace                      |         |          |                | 10<br>11<br>12<br>13 |

Table 1 — continued

| Component         | Qty. | Rating              | Type                     | Part No. |

|-------------------|------|---------------------|--------------------------|----------|

| Resistors         |      |                     |                          |          |

| R1                | 1    | 20 ohms             | AW.3115                  |          |

| R2                | 1    | 22 ohms             | AW.2115                  |          |

| R3                | 1    | 27 ohms             | AW.3115                  |          |

| R4 and R5         | 2    | 56 ohms             | ERIE.8                   |          |

| R6                | 1    | 1K ohms             | ERIE.8                   |          |

| R7                | 1    | 1.5K ohms           | 8                        |          |

| R9 and R15        | 2    | 33 ohms             | 8                        |          |

| R10, R14 and R19  | 3    | 680 ohms            | 8                        |          |

| R11 and R16       | 2    | 33 ohms             | AW.3115                  |          |

| R12 and R17       | 2    | 150 ohms            | AW.3115                  |          |

| R18               | 1    | 12K ohms            | 8                        |          |

| Capacitors        |      |                     | a .                      |          |

| C1                | 1    | $0.25 \mu F, 500V$  | B410                     |          |

| C2, C4, C5 and C6 | 4    | $1 \mu F$ , 150V    | B503 Ky                  |          |

| C3                | 1    | $0.1 \ \mu F, 750V$ | B413                     |          |

|                   |      |                     | (selected to $\pm 5\%$ ) |          |

| C7                | 1    | 50 μF, 12V          | 472/LWA/106BA            |          |

| Plug              |      |                     |                          |          |

| PL.1              | 1    |                     | C10-20P                  |          |

### Magnetic amplifiers

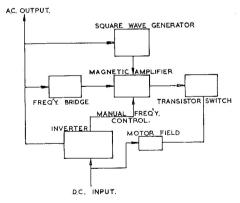

- 4. The two magnetic amplifiers are similar, each consisting of a transductor (T3 and T4) and a pair of diodes (D10-D11 and D12-D13). Their function is to sense and amplify variations in the voltage and frequency of the inverter output and in conjunction with a square wave generator, to apply positive pulses to two pairs of switching transistors.

- 5. Each transductor has three windings, namely the control winding (A1-A2). the bias winding (A3-A4) and the a.c. winding (B1-B2 and B3-B4). The a.c. winding is supplied in push-pull with the square waveform output of the secondary winding of transformer T2. The current due to this output is rectified by the relevant pair of diodes and passes through a load resistor and the a.c. winding, assisting the magnetizing effect of the control winding.

- **6.** The control and bias windings of the transductors are wound in opposition and are

- supplied with direct current from their associated bridge and manual control circuits respectively. The magnetizing effect of the bias and control windings on the transductor core is dependent on the resultant of the two opposing currents and during the period that the flux due to this current is insufficient to cause saturation, the major part of the output from the secondary of transformer T2 is borne by the transductor winding.

- 7. When the transductor core is saturated, the major part of the square wave output is developed across the relevant load resistor (R11 or R16). The time taken for the core to saturate depends upon the manual setting of the voltage or frequency controls and on the output of the inverter. The degree of saturation determines the width of the pulse across the load resistor.

## Switching transistors

**8.** Two pairs of OC.28 transistors (Tr.3–Tr.4 and Tr.5–Tr.6) are bolted direct to the

## Introduction

1. The Type 49 control panel is a transistorized unit designed to control the voltage and frequency of the Royal Inverter, Type 4F which provides a nominal 115V, 400 c/s, single-phase output from a 26V to 29V d.c. supply. The control panel regulates the r.m.s. voltage of the inverter to  $\pm 2.5$ V and the frequency to within  $\pm 10$  c/s of their nominal values. Information on the Royal inverter Type 4F is contained in A.P.4343F, Vol. 1, Sect. 8.

## DESCRIPTION

### General

2. The components of the control panel are enclosed within a rectangular light alloy case

attached to the top of the inverter frame by three anti-vibration mountings. All the components are mounted on insulating boards with the exception of the transistors and Zener diodes which are temperature sensitive. The casings of the transistors serve as heat sinks and are secured to the outside of the chassis; the Zener diodes are of a type in which the anode is a screwed stud and is mounted on a bracket in the case.

3. Cooling is provided by the circulation of air from the inverter fan. The electrical connections on the control panel are taken to a 10-pole fixed plug mounted at one end of the casing. The components together with their ratings and reference numbers are listed in Table 1.

Table 1

Details of components

| Component                                                                | Qty.                           | Rating | Туре   | Part No.  |

|--------------------------------------------------------------------------|--------------------------------|--------|--------|-----------|

| Transformers                                                             |                                |        |        |           |

| T1                                                                       | 1                              |        |        | 64/1031-4 |

| T2                                                                       | 1                              |        |        | 64/1031-5 |

| T3                                                                       | 1                              |        |        | 64/1031-7 |

| Transductors                                                             |                                | g 9    | *      |           |

| T3 and T4                                                                | 2                              |        |        | 64/1031–6 |

| Saturable reactors                                                       |                                |        |        | ,         |

| L1                                                                       | 1                              |        |        | 64/1031-8 |

| L2                                                                       | 1                              |        |        | 64/1031-9 |

| Transistors                                                              |                                |        |        |           |

| Tr.3 Tr.4 Tr. 5 and Tr. 6                                                | 4                              |        | OC.28  | -         |

| Tr.1 and Tr.2                                                            | 2                              |        | OC.36  |           |

| Diodes                                                                   |                                |        |        |           |

| D1, D2, D3, and D4                                                       | 4                              |        | Z.522  |           |

| D7, D8, D9, D10, D11, D12<br>D13, D14, D15, D16, D23<br>D24, D25 and D26 | $\left\langle ,\right\rangle $ |        | ZR.11  | i.        |

| D21 and D22                                                              | 2                              |        | ZR.20R |           |

| Zener diodes                                                             |                                |        |        |           |

| D5 and D6                                                                | 2                              |        | SZ.22B |           |

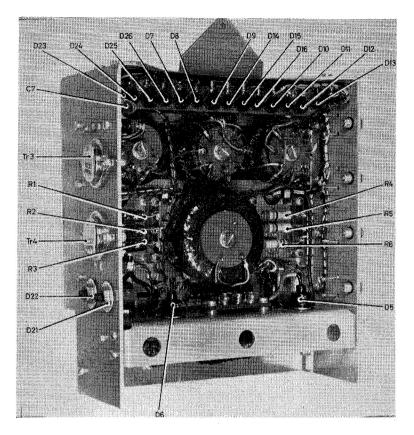

Fig. 3. Control panel chassis—Top

side of the metal chassis and are connected in series with the motor shunt field and the a.c. excitation field of the inverter respectively. The transistors are biased to be normally in the on or conducting condition by the d.c. output of the rectifier bridge (D23, D24, D25 and D26). During the period between starting up and the inverter reaching normal speed, similar bias is provided through the diodes D7, D8, D9 and D14, D15, D16.

9. When the core of a transductor becomes saturated, the resultant positive pulse across the associated load resistor applies a reverse bias to the transistors which causes them to revert to the OFF state for the duration of the pulse. The intermediate transistor in each pair (Tr.4 and Tr.6) is included to improve the rise time of the switching waveform and to reduce the loading on the magnetic amplifier.

## Square wave generator

10. The square wave generator consists of two OC.36 transistors, mounted adjacent to one of the pairs of switching transistors on the side of the chassis, connected as shown in fig. 10 to the primary winding of transformer T2 and the secondary winding of T1. The two transistors are insulated from the metal of the chassis by mica washers. The primary winding of transformer T1 is supplied with 29V, 400 c/s, a.c. through a step-down transformer; the alternating bias applied to the bases of the transistors causes a square waveform to be developed across the collector loads formed by the centre-tapped primary of transformer T2. A Zener diode (D6) is included in the emitter circuit of both transistors to stabilize the peak output waveform. The output from the secondary winding of transformer T2 has a frequency of 800 c/s.

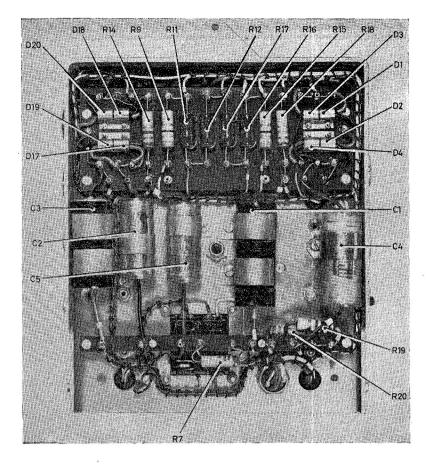

Fig. 4. Control panel chassis—Underside

## Electrical circuits

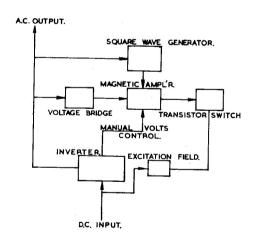

- 11. Referring to the theoretical circuit diagram at fig. 10, the circuit comprises two main sections.

- (1) The voltage control circuit associated with the a.c. excitation field of the inverter.

- (2) The frequency control circuit associated with the shunt field of the inverters d.c. motor.

- 12. Manual adjustment of the inverter output voltage and frequency is provided through two pre-set resistors mounted at the end of the inverter frame, through which direct current is supplied to the bias windings of the transductors. The motor and excitation fields are both supplied from the d.c. input to the inverter, the circuit being completed through the switching transistors referred to in para. 8.

13. Protection for the transistors against the voltage induced across the field windings when the circuits are interrupted by their switching operations is provided by two diodes (D21 and D22) which are connected across their respective field windings. The diodes are normally biased in the reverse direction by the direct current input to the field windings but induced voltages of values higher than that of the supply voltage will cause the diodes to conduct thus preventing voltages in excess of the normal supply being applied to the emitters of Tr.3 and Tr.5.

### **OPERATION**

## General

14. The motor and excitation field currents are interrupted by the action of the switching transistors at a frequency of 800 c/s. The ratio of the ON to the OFF times of the switching transistors, which varies with the inverter

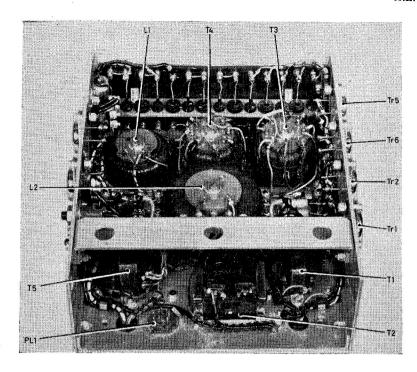

Fig. 5. Control panel chassis—End

output, is used to regulate the field currents to a mean value and thus maintain the output voltage and frequency within prescribed limits.

## Voltage control

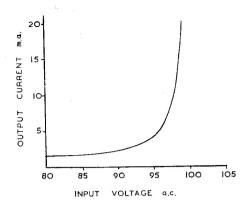

15. The 400 c/s output of the inverter is connected through a saturable reactor (L1) to a full-wave rectifier bridge formed by four diodes (D1, D2, D3 and D4). The output current from the saturable reactor (fig. 7) rises sharply as the core approaches saturation and causes a corresponding increase in the direct current output from the bridge through the control winding (A1–A2) of the transductor T3.

16. The square wave output from the secondary winding of transformer T2 is rectified by the diodes D10 and D11 and applied to the a.c. windings (B1, B2, B3 and B4) of transductor T3 and the load resistor R16. The control and bias windings of the transductor are wound in opposition to each other and the resultant flux, in conjunction

with the flux produced by the square wave output, determines the degree of saturation of the transductor core and hence the width of the pulses across the load resistor.

Fig. 6. Block diagram of voltage control circuit

Fig. 7. Typical characteristic curve for saturable reactor L1

17. During the periods that the transductor core is not saturated, most of the output from the square wave generator is borne by the transductor windings. When the core becomes saturated, the impedance of these windings falls to a low value and practically the whole of the square wave output is developed across the load resistor R16. The waveform appears across the load resistor as positive going pulses with a frequency of 800 c/s which cause the switching transistors Tr.5 and Tr.6 to be biased in the reverse direction and consequently switched to the OFF condition for the duration of the pulse.

## Frequency control

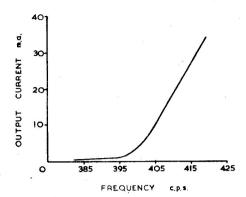

18. The frequency control circuit is basically similar to that used to control the voltage. A rectifier bridge formed by four diodes (D17, D18, D19 and D20) is supplied with a.c. through the transformer T5 and is tuned to approximately 400 c/s by the reactor (L2) together with capacitors C1–C3 and the resistor R18. As L2 and C3 form a series tuned circuit, the impedance decreases as resonance is approached and the current output from the bridge, through the control winding (A1–A2) of the transductor (T4) increases accordingly. The output is filtered by capacitors C2–C5 and resistor R14 to remove the sinusoidal peaks.

19. The magnetic amplifier comprising transductor T4 and the two diodes D12 and D13 functions in a manner similar to that of the voltage amplifier with the exception that the core flux of the transductor T4 decreases with an increase of output from the frequency bridge. This is due to a reversal of the currents in the control and bias windings so as

to pre-polarize the core in the reverse direction. Consequently the width of the output pulses is decreased with a higher frequency output from the inverter.

20. The output pulses from the magnetic amplifier are applied across the load resistor R11 to control the switching transistors Tr.3 and Tr.4, the function of the switching circuit being identical to that of the voltage control but the ratio of the on to the OFF time of the switching transistors is in the opposite sense. Thus an increase in frequency will cause a reduction in the pulse width as stated at para. 20, the strength of the motor shunt field will be increased thereby reducing the motor speed and the output frequency.

## **SERVICING**

# Output voltage and frequency tests

21. Periodic tests should be made of the inverter output voltage and frequency in accordance with the relevant Servicing Schedule. The voltage should be measured with a Testmeter, Type D and the frequency with a 300 to 500 c/s frequency meter such as 5QP/154, or suitable equivalents. Each measurement should be made between the A.C. OUTPUT and the EARTH terminals and where necessary the manual controls should be adjusted to give 117V (r.m.s.) output at a frequency of 403 c/s with a d.c. input between 26 and 29 volts.

## **Fault location**

22. If the control panel should become unserviceable, the cover should be removed and a visual check made for obvious faults such as broken connections or poorly soldered joints.

Fig. 8. Block diagram of frequency control circuit

Fig. 9. Typical output characteristic of frequency bridge

## Note . . .

The circuit should NOT be tested for continuity with an ohmmeter in the usual manner because of the possibility of causing damage to the transistors. For similar reasons insulation resistance testing is not permissible.

- 23. Complete access to all the components of the control panel cannot be gained whilst the panel is mounted in the inverter frame. Units authorized to effect repairs should therefore remove the panel from the inverter before attempting to renew an unserviceable component.

- 24. The control panel may be removed by firstly removing the four screws securing the inverter cover, and after taking off the cover, disconnecting the cable and socket connections before removing the centre screw from

each of the three anti-vibration mountings. The control panel may then be lifted from the inverter frame.

25. The panel can be dismantled without the use of special tools but great care is necessary in the use of soldering irons. Soldering operations should be completed as quickly as possible to avoid the conduction of heat to semi-conductor components.

## Transistors and diodes

- 26. When soldered connections to transistors or diodes are made or removed, the wire between the body of the device and the connection should be held in a pair of smooth jawed pliers until the joint has cooled sufficiently to prevent heat being applied to the component.

- 27. The casings of the four OC.28 transistors (Tr.3, 4, 5 and 6) serve as heat sinks and it is therefore essential that they are in good metallic contact with the brackets to which they are secured. The OC.36 transistors (Tr.1 and 2) used in the square wave generator are insulated from the chassis by mica washers. The screwed metal studs of diodes D5, D6, D21 and D22 form anode connections and must therefore make good contact with the chassis.

### Capacitors

28. The capacitors which are secured by clips should be wound with layers of tape so that the clips hold them firmly in position. Should it become necessary to replace capacitor C3, a Hunts, Type B.413 should be used of a value selected to  $0.1 \mu F \pm 5\%$ .